磁羅盤的測量原理:

Arduino應用與實驗設置:

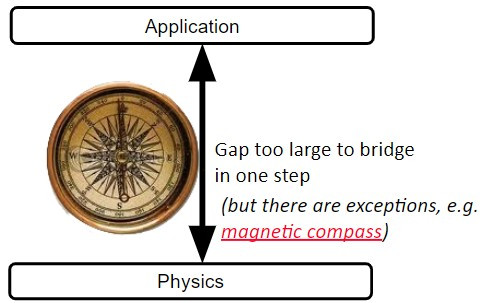

| 層次 | 說明 |

|---|---|

| Application | 應用層,使用者直接互動的軟體層,如手機應用和桌面應用。 |

| Algorithm | 應用程式背後的計算邏輯和流程,用於解決具體問題。 |

| Programming Language | 程式語言,如 C、Python、Java。 |

| Operating System/Virtual Machines | 操作系統和虛擬機,提供應用程式與硬件之間的接口。 |

| Instruction Set Architecture (ISA) | 指令集架構,定義軟體和硬體之間的指令集。 |

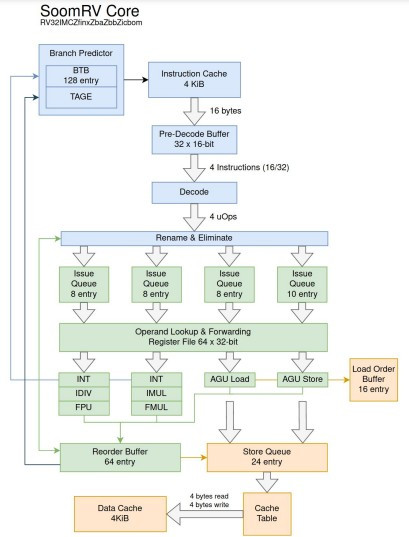

| Microarchitecture | 微架構,實現指令集的具體硬件設計,如處理器內部結構。 |

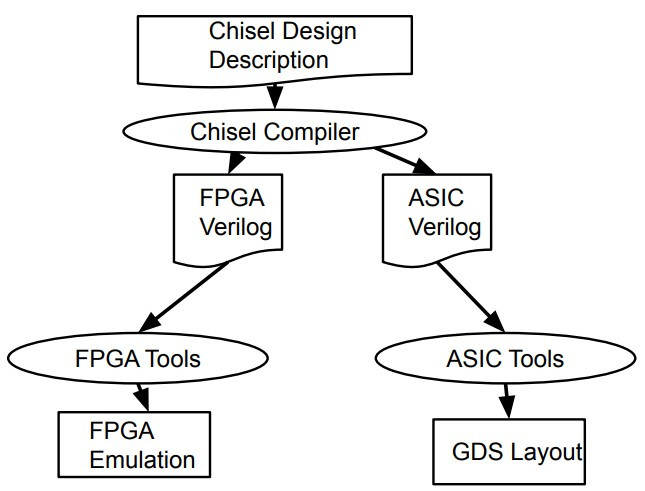

| Gates/Register-Transfer Level (RTL) | 閘級/寄存器傳輸級,硬件描述層,用於設計邏輯閘電路和數據傳輸。 |

| Circuits | 電路層,包括電晶體和其他基本電子元件的組合。 |

| Devices | 設備層,如處理器、記憶體晶片等基本硬件元件。 |

| Physics | 物理層,最底層的技術層,包括半導體製造和電信號傳輸。 |

每一層都對上層提供支持和抽象,這使得應用程序可以有效地運行在不同的硬件上。這種層次化設計允許開發者專注於更高層的邏輯設計,而不必深入到底層硬件的具體實現細節。

ISA 是計算機架構的基礎,它定義了軟件與硬件之間的接口:

von Neumann 規定了計算機如何執行指令並管理狀態: